The implementation of the current FPGA algorithm has the following methods:

1. Development of the Verilog/VHDL language;

2. system generator;

3. The ImpulsC compiler implements from C code to HDL language;

4. Vivado HLS.

This article focuses on the configuration of the second method.

System generator

The System generator can be seamlessly connected to ISE or Vivado. But you need a version of the correspondence:

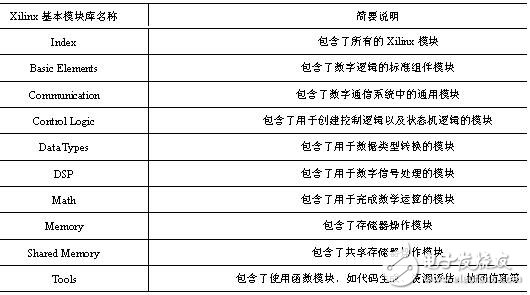

After the System generator is installed, some Xilinx FPGA-specific module libraries will be added to the Simulin module library, including the Basic Element, CommunicaTIon, Control Logic, DataTypes, DSP, Math, Memory, Shared Momory, Tool and other module libraries. Only the modules here can be used. Perform simulation and synthesis of FPGA algorithms, and so on. Using these modules, you can simply select some modules, and even some lines can automatically generate the HDL code you need, freeing developers from the underlying boring code, and putting more energy into the algorithm, which is perfect. It embodies the idea that tools serve people. ISE14.7, Vavido HLS has been able to generate HDL code using C and C++, which is mainly for Xilinx 7 series FPGAs, which students interested can try. In addition, Matlab2013a adds HDL coder as a stand-alone tool and has been able to support Xilinx FPGAs.

(one). Basic introduction to the Xilinx Blockset library

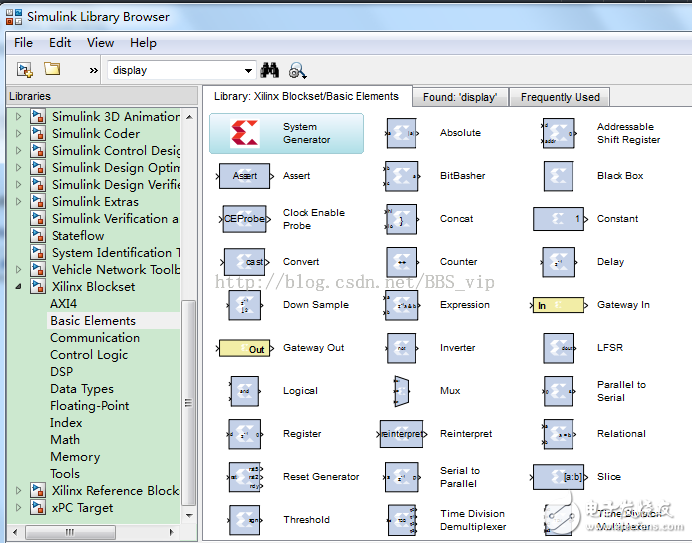

System Generator and Simulink are seamlessly linked and can be launched directly in the MATLAB standard toolbar, as shown in Figure 1-1. These modules are divided into different libraries according to their functions. For ease of use, some of the widely used modules are added to some libraries. All modules are arranged in alphabetical order in the Xilinx Index library. The reader should note that in the Simulink environment, only the system built by the Xilinx module can guarantee the hardware is implementable, and its status is similar to the synthesizable statement in the HDL language.

Figure 1-1 Xilinx DSP Module Set (Xilinx Blockset)

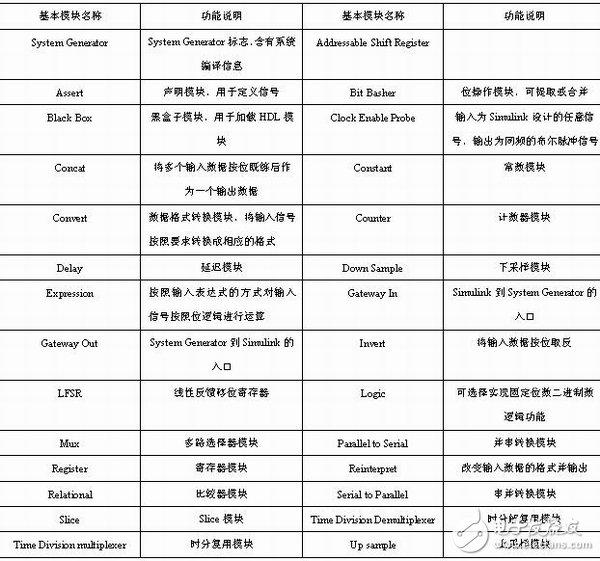

As can be seen from the design flow, familiarity with the Xilinx DSP basic module library is a key part of the design process. Only by mastering the features and functions of the basic module can the algorithm be implemented better. Together with the System Generator, the Xilinx module library generates the optimal logic for Xilinx programmable devices. This is the lowest-level design module and is equivalent to IP Core, with more than 90. A brief description of the Xilinx module library is listed in Table 1-1.

Table 1-1 Brief description of the System Generator library

1. Basic Element Module (Basic Elements)

The base unit module library contains standard component blocks for digital logic that allow you to insert time delays, change signal rates, introduce constants, counters, and multiplexers. In addition, there are three special modules, the System Generator logo, the Black Box module, and the boundary definition module, which will be described in detail later. The brief module descriptions in this library are listed in Table 1-2.

Table 1-2 Description of the basic unit modules

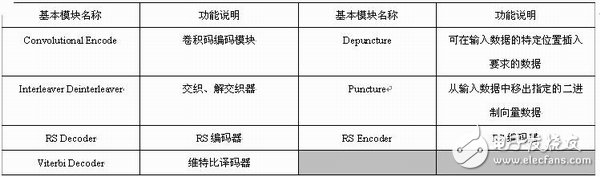

2. Communication module (communicaTIon)

Communication applications are one of the main application areas of FPGAs, so Xilinx's communication module library provides various functions for implementing digital communication, including convolutional codecs, RS codecs, and interleavers. The brief module descriptions in this library are listed in Table 1-3.

Table 1-3 Description of the communication module

3. Control Logic Module

The control logic mainly includes resources for creating various control logic and state machines, including logic expression modules, soft core controllers, multiplexers, and memories. The brief descriptions are listed in Table 1-4.

Table 1-4 Description of the description of the control logic module

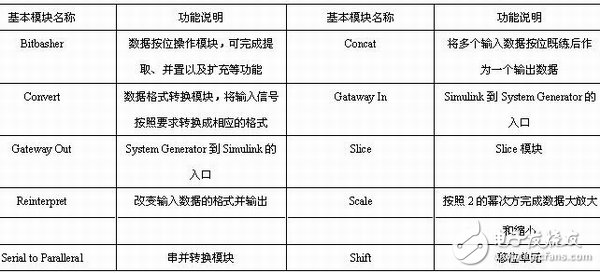

4. Data Types

The data type module is mainly used for data type conversion of signals, including shifting, quantization, parallel/serial, serial/parallel conversion, and precision adjustment modules, and the brief descriptions are listed in Table 1-5.

Table 1-5 Description of the description of the data type module

ZGAR AZ Vape Pods 5.0

ZGAR electronic cigarette uses high-tech R&D, food grade disposable pod device and high-quality raw material. All package designs are Original IP. Our designer team is from Hong Kong. We have very high requirements for product quality, flavors taste and packaging design. The E-liquid is imported, materials are food grade, and assembly plant is medical-grade dust-free workshops.

From production to packaging, the whole system of tracking, efficient and orderly process, achieving daily efficient output. WEIKA pays attention to the details of each process control. The first class dust-free production workshop has passed the GMP food and drug production standard certification, ensuring quality and safety. We choose the products with a traceability system, which can not only effectively track and trace all kinds of data, but also ensure good product quality.

We offer best price, high quality Pods, Pods Touch Screen, Empty Pod System, Pod Vape, Disposable Pod device, E-cigar, Vape Pods to all over the world.

Much Better Vaping Experience!

Pods, Vape Pods, Empty Pod System Vape,Disposable Pod Vape Systems

ZGAR INTERNATIONAL(HK)CO., LIMITED , https://www.szdisposable-vape.com